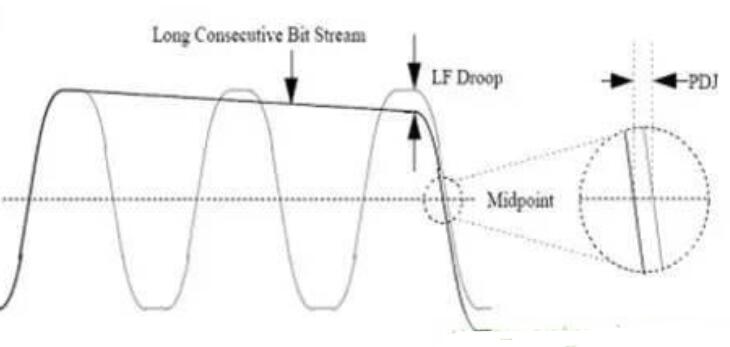

We know that a series of AC coupling capacitors in the series signal can provide DC bias and overcurrent protection, but this will also bring another problem to the link PDJ (Pattern-Dependent Jitter).

The placement of AC coupling capacitors has just been solved, and now we have encountered the value selection problem! Obviously, the AC coupling capacitor does not matter in any case.

AC coupling capacitor

We know that connecting an AC coupling capacitor in series with a serial signal can provide DC bias and overcurrent protection, but it also brings another problem to the link, pdj (mode dependent jitter). As the name suggests, it is a matter of type. Our link can be equivalent to a high-pass rc circuit. When there is a continuous “1” or “0”, there will be a DC voltage drop below, which will not only affect the height of the eye, but also cause pdj.

How can I reduce the DC voltage drop? This is related to the rc time constant. The larger the value of Rc, the more DC components passed and the smaller the DC voltage drop. Since the equivalent r is relatively fixed in the link, the value of the coupling capacitor can only be adjusted. The larger the capacitance value, the smaller the voltage drop.

AC coupling capacitor

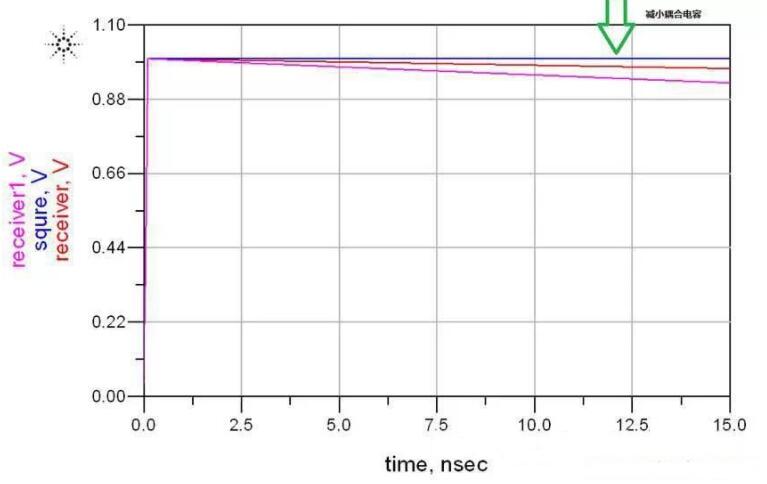

Then let’s increase the capacitance infinitely!

The answer is: No, no!

Because the capacitors actually installed are not their own ideal capacitors, in addition to ESR and ESL, there is also the installation of inductance, so there is a problem with the series resonance frequency of an enterprise. In this process, the capacitance is capacitive before the frequency analysis, and then inductive. The larger the capacitance value, the smaller the resonant frequency, and the capacitance will develop a kind of inductance between lower frequencies, which will cause the attenuation of the signal through high-frequency components to increase, and it may also reduce the eye height The edge becomes slower, and the jitter increases.

Therefore, the above two considerations should be considered when choosing this value.